Let’s discuss the question: how does a cell get min n max delay. We summarize all relevant answers in section Q&A of website Myyachtguardian.com in category: Blog MMO. See more related questions in the comments below.

Table of Contents

What is min delay and max delay?

cell delay depends upon input transition and output fanout. so now we have two path delay values for rise edge and falling edge. greater one is considered as Max delay and smaller one is min delay.

How do you calculate maximum delay?

- In data path : max delay = (2+11+2+9+2)ns=26ns.

- In data path : min delay = (1+9+1+6+1)ns=18ns.

- In clock path: max delay= (3+9+3)ns=15ns.

- In clock path : min delay = (2+5+2)ns=9ns.

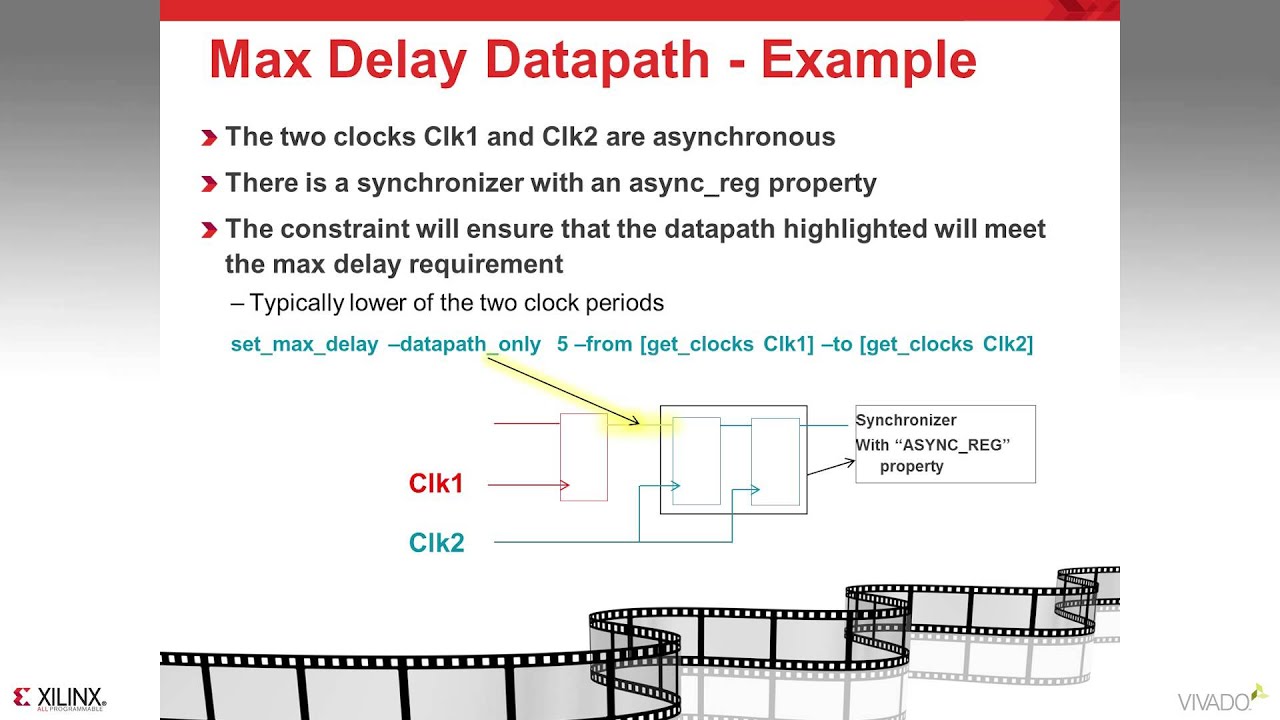

Advanced Timing Exceptions False Path, Min Max Delay and Set Case Analysis

Images related to the topicAdvanced Timing Exceptions False Path, Min Max Delay and Set Case Analysis

How do you calculate cell delay?

For example, if you have a data point (transition, load) = (1.698, 0.2), use data points (1.077, 0.12), (1.077, 0.15), (1.566, 0.12), and (1.566, 0.15) to get a set of A, B, C, and D. Next, insert the data point (1.698, 0.2) to get the cell delay.

What is max delay constraint?

The maximum delay constraint limits the number of consecutive gates on the critical path of a high-speed circuit because a high clock frequency means a short clock period.

What is set min delay?

Allows you to override the default hold constraint for any path with a specific minimum time value for the path. You can specify the source ( -from ), common through elements ( – thru ), and destination ( -to ) elements of the path included in the minimum delay value.

How do you find the minimum clock period?

For the single-cycle CPU, the minimum clock period is simply the sum of the delays through all five sub-components (not stages, as there is only one stage). The assumption that the pipelining overhead is zero means that the minimum clock period of the pipeline CPU is simply the longest individual stage delay.

What is TPD and TCD?

∎ Contamination delay (tcd. ): delay until Y starts changing. ∎ Propagation delay (tpd. ): delay until Y finishes changing.

How do you find the maximum frequency of operation?

The maximum operating frequency of the bus switch type can be calculated based on the rise waveform. Maximum operating frequency ≈ 1/(τ), where τ is a time constant: Since τ is determined by charging and discharging time, τ is calculated from the time required for the output voltage to reaches 63%.

What is a delay cell?

The delay cells respectively include a first to a third logic gate. The first logic gate, in response to a selection signal, generates a first signal based on an input signal. The second logic gate generates a second signal based on the input signal in response to the selection signal.

How is contamination delay calculated?

Assume that data departs the first element as early as possible. Add the shortest possible delay between this departure time and the arrival at the second element; this is called the contamination delay.

What is electronic delay?

Propagation delay in electronic circuits

In this context, propagation delay is defined as the amount of time required after an input signal is applied and has stabilized to the input of a circuit to the time that the output of the circuit has stabilized to the correct output signal. This is symbolized as tpd.

Excel MAX or MIN with CONDITIONS (MAXIFS \u0026 AGGREGATE Method)

Images related to the topicExcel MAX or MIN with CONDITIONS (MAXIFS \u0026 AGGREGATE Method)

What are delay cells in VLSI?

Delay cells: There is another category of special buffers called as Delay cells which generally are used to fix hold with huge magnitude of violations. Delay cells have the same functionality as that of a buffer but with larger delay, larger area and high power.

What is decap cells in VLSI?

Decap cells are basically a charge storing device made of the capacitors and used to support the instant current requirement in the power delivery network.

What is stage delay in VLSI?

Often, it makes sense to combine the calculation of a gate and all the wire connected to its output. This combination is often called the stage delay. The delay of a wire or gate may also depend on the behaviour of the nearby components. This is one of the main effects that is analyzed during signal integrity checks.

What is Set_input_delay SDC?

Defines the arrival time of an input relative to a clock.

What is setup and hold time in VLSI?

Ø Setup Time: the amount of time the data at the synchronous input (D) must be stable before the active edge of clock. Ø Hold Time: the amount of time the data at the synchronous input (D) must be stable after the active edge of clock.

What is VLSI case analysis?

Case analysis is a way to specify a given mode of the design without. altering the netlist structure. For the current timing analysis ses- sion, you can specify either that some signals are at a constant value. (1 or 0) or that only one type of transition (rising or falling) is to.

What are timing exceptions in VLSI?

Timing exceptions allow you to modify the default timing analysis rules for specific paths, such as multicycle paths, false paths, and minimum and maximum delays.

What are clock tree exceptions?

Clock Tree Exceptions

Non- Stop Pin. Exclude Pin. Float Pin. Stop Pin. Don’t Touch Subtree.

What are timing arcs?

Timing Arc represents the timing relationship between 2 Pins of any element or Block or any boundaries. Basically it represents the timing characteristic of the element or block or Boundaries. Timing arc has a Start-point and an Endpoint. The start-point can be an Input, output or inout.

How do you calculate maximum clock speed?

The maximum clock frequency is fc = 1/Tc = 3.33 GHz. The short path also remains the same at 55 ps. The hold time is effectively increased by the skew to 60 + 50 = 110 ps, which is much greater than 55 ps. Hence, the circuit will violate the hold time and malfunction at any frequency.

Min and Max Function in Excel | Functions in Excel | Excel Tutorial Formulas | Learn Excel

Images related to the topicMin and Max Function in Excel | Functions in Excel | Excel Tutorial Formulas | Learn Excel

What is setup and hold time expression?

Setup Time : The minimum time before the active edge of the clock, the input data must remain stable is called the setup time. Hold Time : The minimum time after the active edge of the clock, the input data must remain stable is called the hold time.

How long is a clock cycle?

Clocks do cycle. A Clock Cycle is the amount of picoseconds passed between pulses of a Clock Signal (amount of millimeters a packet of photons propagated). Plus, one can make the cycle 2 times shorter, detecting both rises and falls of the signal.

Related searches

- what are required time arrival time and slack calculation for setup and hold check

- Cell delay in VLSI

- how to fix setup and hold violations

- min delay constraint

- net delay in vlsi

- static timing analysis

- Net delay in VLSI

- Static timing analysis

- max delay constraint

- cell delay in vlsi

- wire load model

- How to fix setup and hold violations

Information related to the topic how does a cell get min n max delay

Here are the search results of the thread how does a cell get min n max delay from Bing. You can read more if you want.

You have just come across an article on the topic how does a cell get min n max delay. If you found this article useful, please share it. Thank you very much.